# GenICam

# **GenCP**

# Generic Control Protocol

Version 1.3

## **Content**

Version 1.3

| Cl        | nange | His    | tory                            | 7  |

|-----------|-------|--------|---------------------------------|----|

| 1.        | Inti  | roduc  | ction                           | 8  |

|           | 1.1.  | Mot    | tivation                        | 8  |

|           | 1.2.  | Obj    | ective                          | 8  |

|           | 1.3.  | Abs    | stract                          | 9  |

|           | 1.4.  | Acr    | onyms                           | 10 |

|           | 1.5.  | Ref    | erences                         | 11 |

|           | 1.6.  | Req    | uirement Terminology            | 11 |

| 2.        | De    | finiti | ons                             | 12 |

|           | 2.1.  | Dev    | vice Description File           | 12 |

|           | 2.2.  | Stri   | ng Encoding                     | 12 |

|           | 2.3.  | Byte   | e and Bit Order                 | 12 |

|           | 2.4.  | Gen    | nCP Version                     | 12 |

|           | 2.5.  | CRO    | C                               | 13 |

| 2.6. Link |       | k      | 13                              |    |

|           | 2.7.  | Cha    | nnel                            | 13 |

|           | 2.7   | .1.    | Default Channel                 | 13 |

| 3.        | Op    | eratio | on                              | 14 |

|           | 3.1.  | Pro    | tocol                           | 14 |

|           | 3.1   | .1.    | Command & Acknowledge Mechanism | 14 |

|           | 3.1   | .2.    | Pending Acknowledge             | 17 |

|           | 3.1   | .3.    | Message Channel                 | 19 |

|           | 3.1   | .4.    | Failure                         | 20 |

|           | 3.2.  | Hea    | urtbeat                         | 25 |

|           | 3.3.  | Gen    | ılCam File                      | 26 |

|           | 3.3   | .1.    | Manifest Table                  | 26 |

|           | 3.3   | .2.    | Retrieval                       | 26 |

|           | 3.3   | .3.    | Compression                     | 26 |

| 4.        | Pac   | cket I | Layout                          |    |

|           |       |        | neral Packet Layout             |    |

| <b>T</b> 7 |      | • | •   |

|------------|------|---|-----|

| 1/00       | sion |   | - 2 |

| VCI        | SICH |   | . ) |

## GenCP Standard

| 4.2. Pre   | efix                                     | 29 |

|------------|------------------------------------------|----|

| 4.3. Co    | mmon Command Data                        | 29 |

| 4.3.1.     | Command Packet Layout                    | 30 |

| 4.3.2.     | Acknowledge Packet Layout                | 31 |

| 4.3.3.     | Command IDs                              | 35 |

| 4.4. Co    | mmand Specific Data                      | 37 |

| 4.4.1.     | ReadMem Command                          | 37 |

| 4.4.2.     | ReadMem Acknowledge                      | 37 |

| 4.4.3.     | WriteMem Command                         | 38 |

| 4.4.4.     | WriteMem Acknowledge                     | 38 |

| 4.4.5.     | Pending Acknowledge                      | 39 |

| 4.4.6.     | ReadMemStacked Command                   | 39 |

| 4.4.7.     | ReadMemStacked Acknowledge               | 40 |

| 4.4.8.     | WriteMemStacked Command                  | 41 |

| 4.4.9.     | WriteMemStacked Acknowledge              | 42 |

| 4.4.10.    | Event Command                            | 44 |

| 4.4.11.    | Event Acknowledge                        | 45 |

| 4.5. Pos   | stfix                                    | 45 |

| 5. Bootsti | rap Register Map                         | 46 |

| 5.1. Ted   | chnology Agnostic Bootstrap Register Map | 46 |

| 5.2. Str   | ing Registers                            | 46 |

| 5.3. Co    | nditional Mandatory Registers            | 46 |

| 5.4. Re    | gister Map                               | 47 |

| 5.4.1.     | GenCP Version                            | 49 |

| 5.4.2.     | Manufacturer Name                        | 49 |

| 5.4.3.     | Model Name                               | 50 |

| 5.4.4.     | Family Name                              | 50 |

| 5.4.5.     | Device Version (Manufacturer specific)   | 51 |

| 5.4.6.     | Manufacturer Info                        | 51 |

| 5.4.7.     | Serial Number                            | 52 |

| 5.4.8.     | User Defined Name                        | 52 |

| 5.4.9.     | Device Capability                        | 59 |

| Version 1.3 | GenCP Standard |

|-------------|----------------|

|             |                |

| 5.4.10. Maximum Device Response Time (MDRT)     | 54 |

|-------------------------------------------------|----|

| 5.4.11. Manifest Table Address                  | 56 |

| 5.4.12. SBRM Address                            | 56 |

| 5.4.13. Device Configuration                    | 57 |

| 5.4.14. Heartbeat Timeout                       | 57 |

| 5.4.15. Message Channel ID                      | 58 |

| 5.4.16. Timestamp                               | 60 |

| 5.4.17. Timestamp Latch                         | 61 |

| 5.4.18. Timestamp Increment                     | 62 |

| 5.4.19. Access Privilege                        | 63 |

| 5.4.20. Protocol Endianess                      | 64 |

| 5.4.21. Implementation Endianess                | 64 |

| 5.4.22. Device Software Interface Version       | 65 |

| 5.5. Generic Tables                             | 65 |

| 5.5.1. Manifest                                 | 65 |

| 1. Serial Port Implementations                  | 69 |

| 1.1. Byteorder                                  | 69 |

| 1.2. Channel ID                                 | 69 |

| 1.3. Packet Size                                | 69 |

| 1.4. Serial Parameters                          | 69 |

| 1.4.1. Default port parameters                  | 69 |

| 1.4.2. Changing port parameters                 | 69 |

| 1.5. Serial Prefix                              | 71 |

| 1.6. Serial Postfix                             | 71 |

| 1.7. Packet failure                             | 71 |

| 1.8. Technology Specific Bootstrap Register Map | 72 |

| 1.8.1. Supported Baudrate                       | 72 |

| 1.8.2. Current Baudrate                         | 74 |

| 1.9. Heartbeat                                  | 75 |

# **List of Figures**

Version 1.3

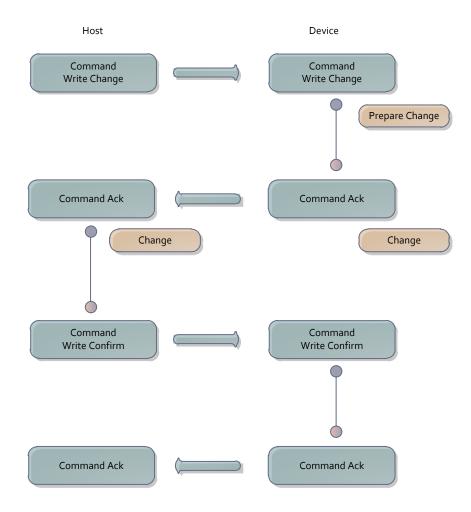

| Fig. 1 - Command Cycle           | 1: |

|----------------------------------|----|

| Fig. 2 – Pending Ack Cycle       |    |

| Fig. 3 – Event Cycle             |    |

| Fig. 4 – Command Failure         |    |

| Fig. 5 – Ack Failure             | 24 |

| Fig. 7 – General Packet Layout   | 2  |

| Fig. 6 - Serial Parameter Change |    |

## **List of Tables**

Version 1.3

| Table 1 - Acronyms                                             | 10 |

|----------------------------------------------------------------|----|

| Table 2 - Event ID                                             |    |

| Table 3 – GenCP Event IDs                                      | 20 |

| Table 4 - Common Command Data                                  | 30 |

| Table 5 - Acknowledge layout                                   | 31 |

| Table 6 – Status Codes                                         | 34 |

| Table 7 – Command Identifier                                   | 36 |

| Table 8 - ReadMem SCD-Fields                                   | 37 |

| Table 9 - ReadMem Ack SCD-Fields                               | 37 |

| Table 10 - WriteMem Command SCD-Fields                         | 38 |

| Table 11 - WriteMem Ack SCD-Fields                             | 38 |

| Table 12 - Pending Ack SCD-Fields                              | 39 |

| Table 13 - ReadMemStacked SCD-Fields                           | 40 |

| Table 14 - ReadMemStacked Ack SCD-Fields                       | 41 |

| Table 15 - WriteMemStacked Command SCD-Fields                  | 42 |

| Table 16 - WriteMemStacked Ack SCD-Fields                      | 43 |

| Table 17 - Event Command SCD-Fields                            | 44 |

| Table 18 - Event Acknowledge SCD-Fields                        | 45 |

| Table 19 - Technology agnostic BRM                             | 48 |

| Table 20 - Register GenCP Version                              | 49 |

| Table 21 - Register Device Capabilities                        | 54 |

| Table 22 - Register Maximum Device Response Time               | 55 |

| Table 23 - Register Manifest Table Offset                      | 56 |

| Table 24 - Register Technology Specific Bootstrap Register Map | 57 |

| Table 25 - Register Device Configuration                       | 57 |

| Table 26 - Register Heartbeat Timeout                          | 58 |

| Table 27 - Register Message Channel ID                         | 58 |

| Table 28 - Register Timestamp                                  | 60 |

| Table 29 - Register Timestamp Latch                            | 61 |

| Table 30 - Register Timestamp Increment                        | 62 |

| Table 31 - Register Access Privilege                           | 63 |

| Table 32 - Register - Implementation Endianess                 | 64 |

| Table 33 – Manifest Table Layout                               |    |

| Table 34 - Manifest Entry Layout                               |    |

| Table 35 - Serial Prefix                                       |    |

| Table 36 - Serial BRM                                          | 72 |

| Table 37 - Register – Serial – Supported Baudrates             | 73 |

| Table 38 - Register – Serial – Current Bandrate                | 74 |

# **Change History**

| Version | Date      | Description                                                                                                                                                 |  |  |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0     |           | 1st Version                                                                                                                                                 |  |  |

| 1.1     | Oct 2014  | Clarification of RequestAck bit.                                                                                                                            |  |  |

|         |           | Added MultipleEvents per Event Command description including capability and enable bit.                                                                     |  |  |

|         |           | Clarify command execution on request_id = 0                                                                                                                 |  |  |

|         |           | Clarify that acknowledges on corrupt command packets                                                                                                        |  |  |

|         |           | Make Heartbeat for devices using GenCP over a serial link mandatory to allow baud rate switching                                                            |  |  |

| 1.2     | Feb 2016  | Renaming of Filetypes to Fileformats and adding new Filetypes for Buffer-XML.  Moving all Serial-Link based paragraphs to an appendix  Removing link to U3V |  |  |

| 1.3     | June 2018 | Stacked RW access                                                                                                                                           |  |  |

| 1.3     | June 2018 | Stacked RW access  Clarification of register Device Version                                                                                                 |  |  |

|         |           | Added register Device Software Interface Version                                                                                                            |  |  |

#### 1. Introduction

#### 1.1. Motivation

Products, which rely on a serial link for communication, implement a wide variety of proprietary control protocols. Most of these protocols are based on ASCII command strings and ASCII responses or even binary protocols. Proprietary protocols can be integrated into GenICam through the GenICam CLProtocol module, assuming the device manufacturer provides a dynamic link library (DLL) for all supported platforms/operating systems. This DLL does the translation between the camera-specific proprietary control protocol and a GenICam compliant register map, which allows the integration of a device into GenICam.

Providing a manufacturer-specific and platform-specific DLL adds cost and effort:

- It has to be maintained for various platforms and OS versions.

- Device features must be added and updated

- The integration of embedded platforms must be taken into account

A more straightforward approach is to provide a read/write register protocol, which can also run on a serial link and do the register map integration in the camera. There would be only one place to change, the camera firmware, in order to introduce new features. There would be *no* platformspecific software needed, which would allow the use of embedded devices as the controlling host. This protocol can be packet based and therefore used on other packet-based technologies as well.

Some devices on the market implement serial protocols in a similar way already. The idea is to propose a common approach for implementing a protocol to give new implementers a hint and maybe to allow a de facto standard in the future.

The original idea was to simplify the CLProtocol implementation by providing a protocol description. Because a protocol can potentially be used on other technologies as well, the definition is kept more generic. It can be adjusted to other technologies however the serial link of Camera Link was the first approach.

## 1.2. Objective

The objective of this document is to describe

- a packet-based protocol to read and write registers in a register-based device

- a Bootstrap Register Map (BRM) to provide basic device information

- access to the device's GenICam file

- the technology specific communication configuration

For example, an ASCII based serial link protocol could be used in the generic CLProtocol module to communicate with a manufacturer's device over the Camera Link's serial link. At boot up, the generic CLProtocol module would allow the configuration of the serial link. A "generic" software could download the GenICam file by accessing the camera's registers. The software can then provide native GenICam (like GigE Vision) access to the device without the need for the camera vendor to provide a platform/operating system-specific software running on the host, implementing the translation between GenICam register access and manufacturer proprietary protocols.

#### 1.3. Abstract

The protocol is packet based. It follows a simple command/acknowledge scheme to provide resend and timeout capabilities, adding minimum overhead.

The Bootstrap Register Map (BRM) resides in a 64-bit register space. The 64 Kbytes starting on address zero contain technology agnostic information like manufacturer name, model name, etc., and provide a directory for technology specific settings.

In order to locate the GenICam file for a device, software would need to retrieve a list of available GenICam files, called the manifest, from the device's register map. The software would then pick the best fitting GenICam file from the list and access via the device's register map.

# 1.4. Acronyms

| Name     | Description                                                                                                                              |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BRM      | Bootstrap Register Map                                                                                                                   |  |  |

| ABRM     | Technology Agnostic Bootstrap Register Map                                                                                               |  |  |

| SBRM     | Technology Specific Bootstrap Register Map                                                                                               |  |  |

| Device   | Device to be controlled, can be any entity, may not be a camera                                                                          |  |  |

| Host     | Controlling Master, can be any entity, may not be a PC                                                                                   |  |  |

| Link     | Connection between a device and a host.                                                                                                  |  |  |

| Channel  | Logic communication channel between two entities. A Channel is always unidirectional.                                                    |  |  |

| Datagram | A single GenCP packet.                                                                                                                   |  |  |

| Entity   | Either the Device or the host                                                                                                            |  |  |

| DRT      | Device Response Time The time a device needs to process a command not including the transfer time for the packet containing the command. |  |  |

| PTT      | Packet Transfer Time Time to transfer a message/command over a link at a given link speed.                                               |  |  |

| URL      | Uniform Resource Locator                                                                                                                 |  |  |

| CCD      | Common Command Data Section within a GenCP command packet which is common to all commands.                                               |  |  |

| SCD      | Specific Command Data Section within a GenCP command packet which is specific to a given command.                                        |  |  |

Table 1 - Acronyms

## 1.5. References

Camera Link AIA Camera Link

GigE Vision AIA GigE Vision

GenICam EMVA GenICam

RFC3986 URL

RFC791 Internet Protocol

# 1.6. Requirement Terminology

Version 1.3 of this document does not yet define a requirement scheme even though it is planned to apply that in future.

#### 2. Definitions

## 2.1. Device Description File

Device Description File means a GenICam compliant XML file describing the register space of a device.

## 2.2. String Encoding

All strings are encoded in ASCII, UTF8 or UTF16 depending on the BRM setting. The endianess of the characters in an encoded string must match the endianess of the containing register map. Strings defined in the bootstrap register map must follow the endianess of the GenCP Protocol. Strings in the device's register map must follow the implementation endianess.

## 2.3. Byte and Bit Order

The order and size of fields within packets are **not** depending on the endianess used. Fields are listed with its byte offset relative to the start of the section within a packet. All fields are byte aligned.

The endianess of all fields in GenCP protocol packets is technology specific and it must match the endianess of the bootstrap registers of the device.

This document does not define or use explicit bit numbers but identifies bits by its offset to the least significant bit. This notation is endian agnostic even though the offset matches the bit numbers of little-endian notations.

The endianess of the non-bootstrap registers is device implementation specific.

For reference, the byte order is described in Appendix B of RFC791.

Unless explicitly stated for a given technology the endianess for GenCP-Implementations is bigendian.

#### 2.4. GenCP Version

The GenCP version this document describes is

Major Version Number 1

Minor Version Number 3

A change in the Major Version Number indicates a significant feature change and a potential break in backward compatibility.

A change in the Minor Version Number indicates minor feature changes, bug fixes, text clarifications and assures backward compatibility.

#### 2.5. CRC

The CRC checksum used on the packets depends on the underlying technology. If the underlying technology already provides a CRC, that service is used. If the underlying technology does not provide a CRC, the checksum is defined in the Appendix.

#### 2.6. Link

A link is the physical end to end connection between a device and a host used for control communication. For example, for Camera Link Medium, despite the fact that there are two cables carrying data, there is only one serial link for the RS232 communication.

Each link can carry multiple logical communication channels. GenCP assumes a single link between a host and a device.

## 2.7. Channel

A channel is a logical communication path between two entities communicating over a link. There may be multiple logical channels on a single link. Each channel is identified by a unique id number. This number is used in the communication between two entities to identify the channel a packet belongs to. This is either part of the protocol layers below the protocol described here or in the PacketPrefix (see chapter 4.2), depending on the technology. This number is called "channel\_id". A channel's communication is unidirectional, meaning that on a single channel, the sender and receiver side for commands and the sender and receiver side for acknowledges are fixed. Different logical channels may have different directions. The protocol also defines packet layouts and the communication scheme between a device and a host. This document assumes that for the master control channel the host is the command sender and the device is the command receiver even though the roles may change in real live.

#### 2.7.1. Default Channel

The default channel (first control channel) is technology dependent. For example, on Ethernet this would be a port number. For another technology it might be an arbitrary number.

## 3. Operation

#### 3.1. Protocol

## 3.1.1. Command & Acknowledge Mechanism

The protocol uses a command/acknowledge pattern. On each channel each entity has a defined role of being either a "command sender and acknowledge receiver" or a "command receiver and acknowledge sender". It is defined in the BRM which channel acts as a command channel from the host to the device, and which channel is used for the opposite direction from the device to the host. The command sender sends a command and waits for the acknowledge packet. The command receiver receives the command, acts according to the command, and sends the acknowledge packet with the result.

The communication on the default communication channel defines the role of an entity. The sender of a command on the default communication channel is called the host. The command receiver on the default communication channel is called the (remote) device.

A command packet contains a number called *command\_id*, which specifies the action to be executed by the receiver and some additional data to be used when executing the command. The command receiver is expected to process the command and return the result to the sender of the command using an acknowledge packet.

There are commands which always need an acknowledge packet (for example ReadMem) and commands where the acknowledge packet is optional (for example WriteMem). The demand for an acknowledge packet is indicated by a bit in the command packet. In case no acknowledge packet is requested, it is recommended for the command sender to wait the Maximum Device Response Time before the next command is sent.

All commands on a channel are sent sequentially. After a command has been sent, the command sender must wait for an acknowledge packet if requested or wait for a timeout and process the failure before the next command may be sent.

Each command is sent with a sequentially incremented request id. This id allows resending a command in case of a failure. A successful communication would follow this schema:

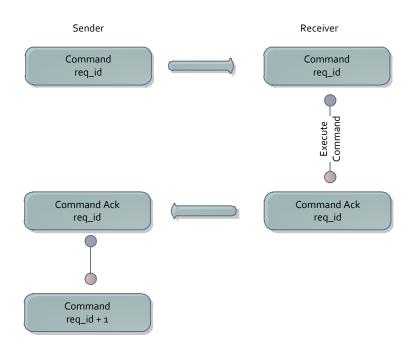

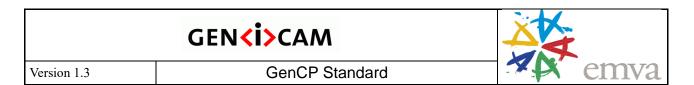

Fig. 1 - Command Cycle

One entity, such as the host, sends a command with a given  $request\_id$  to the other entity, such as the device, on a channel. The device processes the command, if requested forms an acknowledge packet and sends that back to the command sender. Command and acknowledge must have the same request\_id. After the completion of a cycle, a different  $request\_id$  must be used for the next cycle. It is up to the implementation to pick its  $request\_id$ . It is recommended that at the start of a communication the command sender starts with a  $request\_id = 0$  and increments it by 1 with every new command cycle. If the  $request\_id$  wraps around, it is recommended to wrap to 1 in order to prevent a second use of  $request\_id = 0$ . In case the same  $request\_id$  is received a second time in consecutive commands the device should either send a pending ack (see below), if the command is still being processed, or resend the acknowledge in case the final ack for the original command has already been sent.

The exception to the just described "acknowledge resend" rule is  $request\_id = 0$ . For  $request\_id = 0$  it is only allowed to send read commands (for example reading the GenCP Version registers) which do not change the device state. This read command must always be executed because  $request\_id = 0$  and a new ack is to be sent. The data being sent must not come from an "old" cache. In case a  $request\_id = 0$  is sent containing a write command the device must return a GENCP\_INVALID\_PARAMETER status code. Since the host application does not necessarily know which register changes the device's state it is recommended to read register 0 (GenCP)

Version) for that.

This is to prevent that with the start of a communication an application uses  $request\_id = 0$  and sends just 1 command. Then a second application would also start a new communication and would again use  $request\_id = 0$ . In this case it needs to be ensured that the second communication does not get an "old" ack.

The round trip time for a command and the according acknowledge is

Command Transfer Time + Processing Time + Acknowledge Transfer time

When calculating the timeout time for the command cycle, a host must therefore consider:

- the transfer time of the maximum packet size on a given link speed

- the Maximum Device Response Time, which is provided via a bootstrap register

- some margin for technology-dependent delays, which may occur on the link

Reading the Maximum Device Response Time (MDRT) register should not exceed 50 ms in order to guarantee a responsive device. The maximum device response time for any other read or write operation should not exceed 300 ms. This plus the maximum packet transfer time allows the host to calculate a timeout value.

## 3.1.2. Pending Acknowledge

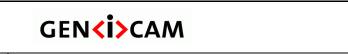

In case the processing of a command takes longer than specified in the Maximum Device Response Time register, the command receiver must send a pending acknowledge. This pending acknowledge response uses the same  $request\_id$  as the command, which triggered it, and provides a temporary timeout in milliseconds to be used only with the command currently executed. The command sender can then temporarily adjust its acknowledge timeout for the current cycle. In case the command receiver has the heartbeat enabled it has to suspend its heartbeat mechanism so that the device does not lose connection. In case the execution of the command takes longer than signaled through an already sent pending acknowledge, the command receiver may issue another pending acknowledge indicating a new, longer timeout.

Fig. 2 – Pending Ack Cycle

In case the device receives a further command packet while processing a command, it reacts as follows:

- If the new command has the same *request\_id* as the command currently processed, another pending acknowledge packet is sent. In this case the pending acknowledge timeout from the original command is used.

- If the new command has a different *request\_id* the device responds with a GENCP\_BUSY status code.

The Processing Time for the inquiry of the Maximum Device Response Time register must not take longer than 50ms.

After the cycle finishes, the host timeout resets to the previously calculated timeout using Maximum Device Response Time and the heartbeat mechanism in the device works as configured before.

## 3.1.3. Message Channel

A Message Channel allows the asynchronous transfer of event commands from the device to the host. For each Message Channel a different channel id from the default channel must be used.

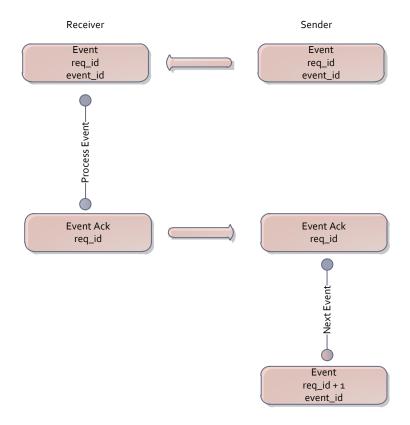

Fig. 3 – Event Cycle

The channel\_id to be used by the Message Channel is set by the host in the according register in the device's BRM. Multiple events can be transmitted in one event command. A single Event is identified by an <code>event\_id</code>. An Event may be accompanied by additional event data. Subsequently sent event commands are identified by <code>request\_ids</code>. One entity, such as the device, sends an event command with a given <code>request\_id</code> to the other entity, such as the host, on a channel. The host acknowledges the event packet by sending an EventAck command back to the device. The event packet and the corresponding acknowledge must have the same <code>request\_id</code>. After the completion of a cycle, a different <code>request\_id</code> for the next cycle must be used. The <code>request\_id</code> follows the schema described in section 3.1.1.

#### 3.1.3.1. Event ID

The source of an event on the Message Channel is identified by an event\_id. An event\_id is a 16-bit value. The bits in this value have the following meaning:

| Bit offset    | Width  | Description                      |  |

|---------------|--------|----------------------------------|--|

| $(lsb \ll x)$ | (bits) |                                  |  |

| 0             | 12     | Event ID                         |  |

|               |        |                                  |  |

| 12            | 2      | Reserved                         |  |

|               |        | Set to 0                         |  |

| 14            | 2      | Namespace                        |  |

|               |        | 0 = GenCP Event ID               |  |

|               |        | 1 = Technology specific Event ID |  |

|               |        | 2 = Device specific Event ID     |  |

Table 2 - Event ID

## 3.1.3.2. GenCP Event ID Codes

| Event ID (Hex) | Name  | Description         |

|----------------|-------|---------------------|

| 0x0000         | Error | Generic Error Event |

Table 3 – GenCP Event IDs

## 3.1.4. *Failure*

A failure on the Command Channel or the Message Channel is discovered through

- a corrupt CCD of a command or acknowledge packet

- a timeout waiting for an acknowledge

- an invalid (too short) packet (timeout waiting for the complete arrival)

- an incorrect packet header

## 3.1.4.1. Corrupt Packet

A packet is corrupt if the transmission of the packet failed (e.g. a transmission failure caused the

CRC of the packet to be wrong or the sender sent the wrong CRC) or if it is too short to carry a correct CCD plus Prefix. In this case the received data is discarded and no answer is sent back to the sender.

The receive buffer should be flushed until no data is received within a maximum packet transfer time or longer.

- The sender must wait after a communication error until all corrupt data is removed and then it sends its command again.

- The receiver discards all corrupt data after a communication error and waits for the sender to resend its command.

- If the underlying technology controls packet handling, it is not necessary to wait for a packet transfer time on failure.

- There is no acknowledge carrying a failure status code in order to prevent the link being flooded with garbage acknowledges.

In case the received Prefix and CCD is correct the receiver must answer as requested with an appropriate status code and the originator can resend the command.

When there are errors on either side, the original command packet is resent from the sender as described in chapter 3.1.4.3.

In case of failure the sender should retry 3 times to transmit the packet.

### 3.1.4.2. Timeout

A packet is considered "too short" if the data for a packet has not completely been received within the Packet Transfer Time (PTT) after the first byte of the packet has arrived. The PTT is depending on

- the link speed

- the maximum packet size allowed on the link

- the timeout for the transfer of two consecutive bytes on a link

If an error occurs on either side, the original command packet is resent from the sender as described in chapter 3.1.4.3.

In case of failure, the sender should retry 3 times to transmit the packet.

## 3.1.4.3. Command Packet Failure

If the command packet is lost on the link or if the command packet is received as corrupt the following actions are supposed to happen:

Fig. 4 – Command Failure

The command is resent after the timeout period with the CommandResend bit being set. The

request id is the same as with the original command.

There is a corner case if the device was opened and only one single command was sent or if the request\_id got a wraparound to 0, the device was closed and a new application starts with request\_id being 0. In this case the CommandResent bit would not be set but the receiver should not discard the command. Therefore, commands with request\_id equals 0 must always be read and must always be executed.

If a received command is invalid (combination of command and flags) or is not supported/unknown by the receiver but at least the CCD is correct (guaranteed by the underlying technology or by CRC) so that the content of the packet is as sent by the originator and the RequestAck bit is set in the flags field an acknowledge must be sent back with the following content:

- the status code is to be set to GENCP\_INVALID\_HEADER or GENCP\_NOT\_IMPLEMENTED (see 4.3.2.1)

- the command\_id is copied from the received packet and the acknowledge flag (see 4.3.3) is set

- the length is set to 0, the SCD is discarded

- the request id is copied from the received packet and left untouched

- CRCs (if existing) must be adjusted

and then it is sent back to the originator.

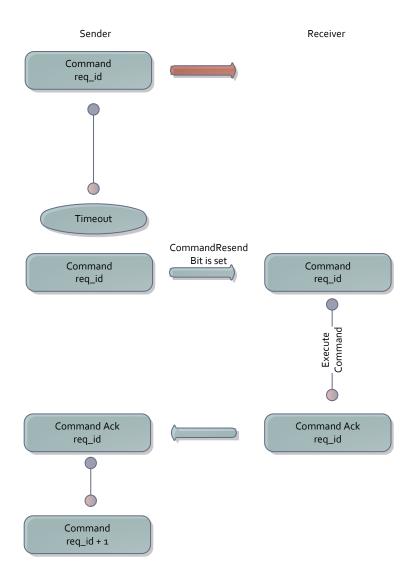

## 3.1.4.4. Acknowledge packet failure

If an acknowledge packet is lost on the link, if the CRC of the acknowledge packet is corrupt or if the content is not as expected, the following actions are supposed to happen:

The resend of the command packet uses the same request\_id as the original. This allows the receiver to identify a resend in case the request\_id is already processed. In this case the command must not be processed again but the previous result should be resent.

Fig. 5 – Ack Failure

In case of a corrupt acknowledge packet the sender may issue the command resend immediately without waiting for the timeout.

## 3.1.4.5. Pending Acknowledge Packet Failure

There are two possible failure cases using pending acknowledge.

- A complete pending acknowledge packet is lost. In this case the sender will generate a timeout as if the pending acknowledge would not have been sent and it will issue a resend of the command packet with the same *request\_id*. Following chapter 3.1.2, the receiver will reissue a pending acknowledge packet.

- A pending acknowledge packet is received corrupt by the sender. This will trigger a resend of the command packet.

## 3.2. Heartbeat

In order to maintain control in case of an unexpected abrupt detach of the controlling application, a watchdog timer is implemented in the device. This mechanism is called Heartbeat. On start-up of the command sender application, the Access Privilege Register in the device's BRM must be set. With that the Heartbeat timer in the device starts. This Heartbeat timer has to be triggered periodically by a read/write register access from the host to the device. The timeout of the Heartbeat can be adjusted through a register in the bootstrap register map. The presence of a Heartbeat mechanism is indicated by a bit in the device capability register in the device's BRM. It may be disabled through a bit in the device configuration register in the BRM.

In case the Heartbeat counter is not triggered by a register access longer than specified in the Heartbeat Timeout register, the device stops streaming and resets the access privilege status and resets communication parameters. After a Heartbeat timeout it should be possible to communicate with a device using default communication parameters for example the baud rate of serial devices. It is technology dependent which parameters are affected.

The Access Privilege register can be set to

time.

- Available The device is available. The device does not stream data.

- Open (Exclusive) Only the controlling application has read and write access to the device.

It is depending on the technology how this is observed. Other applications/hosts will receive an error trying to access the device's register map.

The exception to this rule is the Access Privilege register itself. This register can be read any

When the host changes the state of the Access Privilege register from Open (Exclusive) to Available the device must switch back to default communication parameters after the acknowledge for the write command was sent. The behavior is the same as if the Heartbeat Timeout would run out. This is to allow another application to establish a communication with the device.

#### 3.3. GenlCam File

A GenCP device must be register based. A manufacturer must provide access to a GenICam file describing the register map of the device.

The GenICam file must be stored within the device so that it can be retrieved by the host. The file may be stored and delivered either in uncompressed or compressed format. In case it is compressed it is up to the controlling host to deflate the file.

#### 3.3.1. Manifest Table

A GenCP device may provide multiple GenICam files complying with different GenICam Schema versions. A so called "Manifest Table" register block contains a list of entries, providing information like file versions, complying schema versions, and register addresses. A description of the Manifest register block can be found in the Bootstrap Register Map section of this document.

#### 3.3.2. Retrieval

It is the responsibility of the host software to retrieve the file from the device reading the device's register space using the GenCP Protocol.

## 3.3.3. Compression

The compression methods used in case the GenICam file is stored in the device in a compressed format are DEFLATE and STORE of the .zip file format. File extension for compressed files is zip.

# 4. Packet Layout

The protocol defines the communication between two entities. An entity is either a device or a host. The role of a device and host are defined by the initiator of the default communication. The host is the initiator of the communication on the default channel (see chapter 2.7) and the device responds to that.

## 4.1. General Packet Layout

The generic packet layout is divided into four parts:

Fig. 6 – General Packet Layout

- Prefix describes a technology specific section of the packet. This section covers

- Addressing

- Protocol type identification

- CRC

- channel id etc.

If compared to UDP/IP a prefix would be omitted since everything is covered by the

underlying protocol. For a serial connection, we would not need to cover addressing because it is not part of the technology. We need to identify a communication channel (by channel id) and we need a CRC and we need a preamble to identify the protocol.

- The Common Command Data section contains data which describes the command. For example, this section contains the actual command identifier and the request id.

- The Command Specific Data section is technology agnostic. It carries data which is specific for a given command. For example, for a read command it would contain the address to read from and the number of bytes to read.

- The Postfix section is technology specific. It carries for example a CRC Checksum in case it is needed for a given technology. This section is only mandatory if defined for a given technology.

#### 4.2. Prefix

In case the underlying technology does not provide an addressing schema for multiple communication channels or does not provide a checksum mechanism the protocol needs to provide such services. A packet then contains not only command specific data but also has to mimic an addressing scheme between the device and host. Also we need to be able to support multiple communication channels on a given Link and a checksum.

In case such services are provided by the underlying technology the Prefix can simply be omitted.

#### 4.3. Common Command Data

The Common Command Data section is technology agnostic.

# 4.3.1. Command Packet Layout

| Width (Bytes) | Offset (Bytes) | Description                                                            |           |                                                 |  |  |

|---------------|----------------|------------------------------------------------------------------------|-----------|-------------------------------------------------|--|--|

|               | Prefix         |                                                                        |           |                                                 |  |  |

| 2             | 0              | flags                                                                  |           |                                                 |  |  |

|               | Ü              |                                                                        | /4:~-1-1  |                                                 |  |  |

|               |                | the specific con                                                       |           | ommand options or to provide additional info on |  |  |

|               |                | the specific con                                                       | illialia. |                                                 |  |  |

|               |                | Bit offset                                                             | Width     | Description                                     |  |  |

|               |                | (lsb << x)                                                             | (bits)    |                                                 |  |  |

|               |                | 0                                                                      | 14        | Reserved, set to 0                              |  |  |

|               |                | 14                                                                     | 1         | RequestAck                                      |  |  |

|               |                |                                                                        |           | If set the sender requests an acknowledge       |  |  |

|               |                | 1.7                                                                    |           | packet from the command receiver.               |  |  |

|               |                | 15                                                                     | 1         | CommandResend                                   |  |  |

|               |                |                                                                        |           | If set the command is sent as a retry of a      |  |  |

|               |                | previous sent that failed.                                             |           |                                                 |  |  |

| 2             | 2              | command_id                                                             |           |                                                 |  |  |

|               |                | command_id as specified in the Command ID chapter 4.3.3                |           |                                                 |  |  |

| 2             | 4              | length                                                                 |           |                                                 |  |  |

|               |                | Length of the Specific Command Data depending on the command ID not    |           |                                                 |  |  |

|               |                | including Prefix, Postfix and CCD                                      |           |                                                 |  |  |

| 2             | 6              | request_id                                                             |           |                                                 |  |  |

|               |                | Sequential number to identify a single command. This id is provided by |           |                                                 |  |  |

|               |                | the command sender and incremented every time a new command is         |           |                                                 |  |  |

| issued.       |                |                                                                        |           |                                                 |  |  |

| SCD           |                |                                                                        |           |                                                 |  |  |

|               | Postfix        |                                                                        |           |                                                 |  |  |

Table 4 - Common Command Data

# 4.3.2. Acknowledge Packet Layout

| Width (Bytes) | Offset (Bytes) | Description                                                                                                                                            |  |  |

|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               | Prefix         |                                                                                                                                                        |  |  |

| 2             | 0              | status code                                                                                                                                            |  |  |

|               |                | Status code, indicating the result of the operation. See chapter 4.3.2.1 for a list of codes.                                                          |  |  |

| 2             | 2              | command_id                                                                                                                                             |  |  |

|               |                | Command id as specified in the <i>command_id</i> chapter 4.3.3                                                                                         |  |  |

| 2             | 4              | length                                                                                                                                                 |  |  |

|               |                | Length of the Specific Command Data depending on the command in bytes.                                                                                 |  |  |

| 2             | 6              | request_id                                                                                                                                             |  |  |

|               |                | Sequential number used to identify a single acknowledge. This id is provided by the command sender and incremented every time a new command is issued. |  |  |

| SCD           |                |                                                                                                                                                        |  |  |

| Postfix       |                |                                                                                                                                                        |  |  |

Table 5 - Acknowledge layout

## 4.3.2.1. Status Codes

This section lists status codes that can be returned through an acknowledge packet. Each status code has 16 bits. The bits within the Status Code have the following meanings:

| Bit offset    | Width  | Description                  |

|---------------|--------|------------------------------|

| $(lsb \ll x)$ | (bits) |                              |

| 0             | 12     | Status Code                  |

| 12            | 1      | Reserved                     |

|               |        | Set to 0                     |

| 13            | 2      | Namespace                    |

|               |        | 0 = GenCP Status Code        |

|               |        | 1 = Technology specific Code |

|               |        | 2 = Device specific Code     |

| 15            | 1      | Severity                     |

|               |        | 0 = Warning/Info             |

|               |        | 1 = Error                    |

Warning and Info Status Codes indicate that the command was correctly executed and that the device resumes operation. For example, if a float value needed to be rounded it would be a warning but the rounded value has been set.

| Status Code<br>(Hex) | Name                    | Description                                                                                                                                                                                                                               |

|----------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000               | GENCP_SUCCESS           | Success                                                                                                                                                                                                                                   |

| 0x8001               | GENCP_NOT_IMPLEMENTED   | Command not implemented in the device. This covers for example - Unknown/Unsupported command_id                                                                                                                                           |

| 0x8002               | GENCP_INVALID_PARAMETER | At least one command parameter of CCD or SCD is invalid or out of range. This covers for example:  - CCD-Length field which does not fit to the SCD-Part  - Invalid content of the reserved field in the SCD  - Write with request_id = 0 |

| 0x8003               | GENCP_INVALID_ADDRESS   | Attempt to access a not existing register address.                                                                                                                                                                                        |

| 0x8004               | GENCP_WRITE_PROTECT     | Attempt to write to a read only register.                                                                                                                                                                                                 |

| 0x8005               | GENCP_BAD_ALIGNMENT     | Attempt to access registers with an address which is not aligned according to the underlying technology.                                                                                                                                  |

| 0x8006               | GENCP_ACCESS_DENIED     | Attempt to read a non-readable or write a non-writable register address.                                                                                                                                                                  |

| 0x8007               | GENCP_BUSY              | The command receiver is currently busy.                                                                                                                                                                                                   |

| 0x800B               | GENCP_MSG_TIMEOUT       | Timeout waiting for an acknowledge.                                                                                                                                                                                                       |

|             |                |   | A |  |

|-------------|----------------|---|---|--|

| Version 1.3 | GenCP Standard | X | X |  |

| X | X. |      |

|---|----|------|

| 7 | X  | emva |

| 0x800E | GENCP_INVALID_HEADER | The header of the received command is invalid. This includes CCD and SCD fields but not the command payload. This covers for example:  - Invalid combinations of flags in the CCD-Flags field  - The transmitted packet length does not fit to expected size with the given command and CCD-Length incl. Prefix and Postfix. |

|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x800F | GENCP_WRONG_CONFIG   | The current receiver configuration does not allow the execution of the sent command.                                                                                                                                                                                                                                         |

| •••    |                      |                                                                                                                                                                                                                                                                                                                              |

| 0x8FFF | GENCP_ERROR          | Generic error.                                                                                                                                                                                                                                                                                                               |

Table 6 – Status Codes

### 4.3.3. Command IDs

This chapter describes the *command\_id*s for the command field in the Common Command Data section of a GenCP command packet. The layout of a 16bit *command\_id* is as follows:

| Bit offset    | Width  | Description                                                              |  |

|---------------|--------|--------------------------------------------------------------------------|--|

| $(lsb \ll x)$ | (bits) |                                                                          |  |

| 0             | 1      | Acknowledge Flag                                                         |  |

|               |        | - Set this bit to 0 if the <i>command_id</i> belongs to a                |  |

|               |        | command                                                                  |  |

|               |        | - Set this bit to 1 if the <i>command_id</i> is used for an              |  |

|               |        | acknowledgement                                                          |  |

| 1             | 14     | Command Value                                                            |  |

|               |        | Number identifying a single command/acknowledge                          |  |

| 15            | 1      | Custom Command Identifier                                                |  |

|               |        | <ul> <li>Set this bit to 0 to identify a standardized command</li> </ul> |  |

|               |        | value                                                                    |  |

|               |        | <ul> <li>Set this bit to 1 to mark a custom command value</li> </ul>     |  |

Command ids can either identify a command or an acknowledge.

Command\_ids identifying a command must have the LSB cleared.

Command ids identifying an acknowledgement must have the LSB set to 1.

Custom command\_ids must have the most significant bit set (Hex 8xxx) so that they do not collide with future standard extensions.

Standardized command ids are:

| Command Name          | command_id |

|-----------------------|------------|

| READMEM_CMD           | Hex 0800   |

| READMEM_ACK           | Hex 0801   |

| WRITEMEM_CMD          | Hex 0802   |

| WRITEMEM_ACK          | Hex 0803   |

| PENDING_ACK           | Hex 0805   |

| READMEM_STACKED_CMD   | Hex 0806   |

| READMEM_ STACKED_ACK  | Hex 0807   |

| WRITEMEM_ STACKED_CMD | Hex 0808   |

| WRITEMEM_ STACKED_ACK | Hex 0809   |

| EVENT_CMD             | Hex 0C00   |

| EVENT_ACK             | Hex 0C01   |

Table 7 – Command Identifier

## 4.4. Command Specific Data

### 4.4.1. ReadMem Command

Start address and length of any read access is byte aligned unless the underlying technology states different rules.

| Width   | Offset  | Description                    |  |

|---------|---------|--------------------------------|--|

| (Bytes) | (Bytes) |                                |  |

|         |         | Prefix                         |  |

|         |         | CCD (command_id = READMEM_CMD) |  |

| 8       | 0       | register address               |  |

|         |         | 64 bit register address.       |  |

| 2       | 8       | reserved                       |  |

|         |         | Reserved, set to 0             |  |

| 2       | 10      | read length                    |  |

|         |         | Number of bytes to read.       |  |

|         | Postfix |                                |  |

Table 8 - ReadMem SCD-Fields

# 4.4.2. ReadMem Acknowledge

| Width (Bytes) | Offset (Bytes)                     | Description                                                                                                                                                                                      |  |

|---------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               |                                    | Prefix                                                                                                                                                                                           |  |

|               | CCD-ACK (command_id = READMEM_ACK) |                                                                                                                                                                                                  |  |

| X             | 0                                  | Data                                                                                                                                                                                             |  |

|               |                                    | Data read from the remote device's register map. If the number of bytes read is different than the specified in the relating READMEM_CMD the status of the READMEM_ACK must indicate the reason. |  |

| Postfix       |                                    |                                                                                                                                                                                                  |  |

Table 9 - ReadMem Ack SCD-Fields

### 4.4.3. WriteMem Command

Any write access start address and length is byte aligned unless the underlying technology states different rules. The number of bytes to write is deduced through the length field of the CCD header.

| Width   | Offset                          | Description                                                   |  |  |  |

|---------|---------------------------------|---------------------------------------------------------------|--|--|--|

| (Bytes) | (Bytes)                         |                                                               |  |  |  |

|         | Prefix                          |                                                               |  |  |  |

|         | CCD (command_id = WRITEMEM_CMD) |                                                               |  |  |  |

| 8       | 0                               | register address                                              |  |  |  |

|         |                                 | 64 bit register address.                                      |  |  |  |

| X       | 8                               | data                                                          |  |  |  |

|         |                                 | Number of bytes to write to the remote device's register map. |  |  |  |

| Postfix |                                 |                                                               |  |  |  |

Table 10 - WriteMem Command SCD-Fields

# 4.4.4. WriteMem Acknowledge

The WriteMem acknowledge states the result of a WriteMem command.

| Width   | Offset  | Description                                                                                                                                                                           |  |

|---------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (Bytes) | (Bytes) |                                                                                                                                                                                       |  |

|         |         | Prefix                                                                                                                                                                                |  |

|         |         | CCD-ACK (command_id = WRITEMEM_ACK)                                                                                                                                                   |  |

| 2       | 0       | reserved                                                                                                                                                                              |  |

|         |         | This reserved field is only sent if the length_written field is sent with the acknowledge. If it is sent it is to be set to 0.                                                        |  |

| 2       | 2       | length written                                                                                                                                                                        |  |

|         |         | Number of bytes successfully written to the remote device's register map.  The length written field must only be sent if the according bit in the  Device Capability register is set. |  |

|         | Postfix |                                                                                                                                                                                       |  |

Table 11 - WriteMem Ack SCD-Fields

The length field in CCD section of the WriteMem Ack must be set to 0 or 4 depending on the bit in

the Device Capability register. In case the write\_length field (and the 2 reserved bytes) is sent, the length field is to be set to 4. In case the length written field is not sent the length field is 0.

### 4.4.5. Pending Acknowledge

The pending acknowledge informs the sender that the command, sent with the given request\_id, needs more time to execute than stated in the MDRT register. This allows the temporary adjustment of the timeout mechanism on the command sender side. This "new" temporary timeout is only valid for the command referenced by request\_id. Multiple pending acknowledges can be sent consecutively. The start time for the timeout specified is the time when the pending ack is sent assuming that the time needed to transfer the command is roughly known. The timeout is not referring to the time the original command is sent.

| Width   | Offset  | Description                                                                 |

|---------|---------|-----------------------------------------------------------------------------|

| (Bytes) | (Bytes) |                                                                             |

|         |         | Prefix                                                                      |

|         |         | CCD-ACK (command_id = PENDING_ACK)                                          |

| 2       | 0       | reserved                                                                    |

|         |         | Reserved, set to 0.                                                         |

| 2       | 2       | temporary timeout                                                           |

|         |         | Temporary timeout for the command sent with the given request_id. The       |

|         |         | timeout is specified in ms. The reference time/start time for the temporary |

|         |         | timeout is the time the PendingAck is sent.                                 |

| Postfix |         |                                                                             |

Table 12 - Pending Ack SCD-Fields

#### 4.4.6. ReadMemStacked Command

The ReadMemStacked Command allows sending multiple read requests in one packet. The resulting data must not exceed the maximum packet size. Start address and length of any read access is byte aligned unless the underlying technology is not. The count of read commands within the packet n has to be deduced by the receiver using the packet size sent by the transmitter.

| Width   | Offset  | Description |

|---------|---------|-------------|

| (Bytes) | (Bytes) |             |

|         | Prefix                                    |                                                          |  |  |  |

|---------|-------------------------------------------|----------------------------------------------------------|--|--|--|

|         | CCD (command_id = READMEM_STACKED_CMD)    |                                                          |  |  |  |

| 8       | 0                                         | register address 0                                       |  |  |  |

|         |                                           | 64 bit register address of the first data block to read. |  |  |  |

| 2       | 8                                         | reserved                                                 |  |  |  |

|         |                                           | Reserved, set to 0                                       |  |  |  |

| 2       | 10                                        | read length 0 (Len <sub>0</sub> )                        |  |  |  |

|         |                                           | Number of bytes to read from address 0.                  |  |  |  |

| 8       | (1*12)                                    | register address 1                                       |  |  |  |

|         |                                           | 64 bit register address of the second data block.        |  |  |  |

| 2       | 8+(1*12)                                  | reserved                                                 |  |  |  |

|         |                                           | Reserved, set to 0                                       |  |  |  |

| 2       | 10+(1*12)                                 | read length 1 (Len <sub>1</sub> )                        |  |  |  |

|         |                                           | Number of bytes to read from address 1.                  |  |  |  |

|         | T                                         |                                                          |  |  |  |

| 8       | ((n-1)*12)                                | register address n-1                                     |  |  |  |

|         |                                           | 64 bit register address of the last data block to read.  |  |  |  |

| 2       | 8+((n-1)*12)                              | reserved                                                 |  |  |  |

|         |                                           | Reserved, set to 0                                       |  |  |  |

| 2       | 10+((n-1)*12)                             | read length n-1 ( $Len_{n-1}$ )                          |  |  |  |

|         | Number of bytes to read from address n-1. |                                                          |  |  |  |

| Postfix |                                           |                                                          |  |  |  |

Table 13 - ReadMemStacked SCD-Fields

# 4.4.7. ReadMemStacked Acknowledge

The ReadMemStacked acknowledge states the result of a ReadMemStacked command.

| Width (Bytes)    | Offset<br>(Bytes)                          | Description                                      |  |  |

|------------------|--------------------------------------------|--------------------------------------------------|--|--|

|                  | Prefix                                     |                                                  |  |  |

|                  | CCD-ACK (command_id = READMEM_STACKED_ACK) |                                                  |  |  |

| Len <sub>0</sub> | 0                                          | data                                             |  |  |

|                  |                                            | Data read from the remote device's register map. |  |  |

| Len <sub>1</sub>   | Len <sub>0</sub>            | data                                             |  |

|--------------------|-----------------------------|--------------------------------------------------|--|

|                    |                             | Data read from the remote device's register map. |  |

|                    |                             |                                                  |  |

| Len <sub>n-1</sub> | $\sum_{i=1}^{n-2} I_{i}$    | data                                             |  |

|                    | $\sum_{k=0}^{\infty} Len_k$ | Data read from the remote device's register map. |  |

| Postfix            |                             |                                                  |  |

Table 14 - ReadMemStacked Ack SCD-Fields

If the number of bytes read is different than specified in the relating READMEM\_STACKED\_CMD the status of the READMEM\_STACKED\_ACK must indicate the reason. In that case subsequent read requests from the according READMEM\_STACKED\_CMD are not executed by the receiver. The acknowledge only returns the data read correctly.

#### 4.4.8. WriteMemStacked Command

The WriteMemStacked command allows sending multiple write requests in one packet. Any write access start address and length is byte aligned unless the underlying technology states different rules. The number of bytes to write is deduced from the length field of the CCD header. The count of writes n within the packet has to be deduced by the receiver by parsing the packet up to the packet size sent by the transmitter.

| Width (Bytes)    | Offset<br>(Bytes)   | Description                                               |

|------------------|---------------------|-----------------------------------------------------------|

|                  | ( )                 | D (*                                                      |

|                  |                     | Prefix                                                    |

|                  | CCD (comm           | nand_id = WRITEMEM_STACKED_CMD)                           |

| 8                | 0                   | register address 0                                        |

|                  |                     | 64 bit register address of the first data block to write  |

| 2                | 8                   | reserved                                                  |

|                  |                     | Reserved, set to 0                                        |

| 2                | 10                  | length data block 0 (Len <sub>0</sub> )                   |

|                  |                     | Length of the first data block to write in bytes          |

| Len <sub>0</sub> | 12                  | data                                                      |

|                  |                     | First data block                                          |

| 8                | 12+Len <sub>0</sub> | register address 1                                        |

|                  |                     | 64 bit register address of the second data block to write |

| Version 1.3  | GenCP Standard  |

|--------------|-----------------|

| VC151011 1.5 | Julian Guilland |

| 2                  | 20+Len <sub>0</sub>                    | reserved                                                |  |  |

|--------------------|----------------------------------------|---------------------------------------------------------|--|--|

|                    |                                        | Reserved, set to 0                                      |  |  |

| 2                  | 22+Len <sub>0</sub>                    | length data block 1 (Len <sub>1</sub> )                 |  |  |

|                    |                                        | Length of the second data block in bytes                |  |  |

| Len <sub>1</sub>   | 24+Len <sub>0</sub>                    | data                                                    |  |  |

|                    |                                        | Second data block                                       |  |  |

|                    |                                        |                                                         |  |  |

| 8                  | $\sum_{k=1}^{n-2} 12 + Len_k$          | register address n-1                                    |  |  |

|                    | $\sum_{k=0}^{\infty} 12 + Len_k$       | 64 bit register address of the last data block to write |  |  |

| 2                  | n-2                                    | reserved                                                |  |  |

|                    | $8 + \sum_{k=0}^{\infty} 12 + Len_k$   | Reserved, set to 0                                      |  |  |

| 2                  | n-2                                    | length data block n-1 (Len <sub>n-1</sub> )             |  |  |

|                    | $10 + \sum_{k=0}^{\infty} 12 + Len_k$  | Length of the last data block in bytes                  |  |  |

| Len <sub>n-1</sub> | $12 + \sum_{i=1}^{n-2} 12 + I_{i} = 0$ | data                                                    |  |  |

|                    | $12 + \sum_{k=0}^{\infty} 12 + Len_k$  | Last data block                                         |  |  |

|                    | Postfix                                |                                                         |  |  |

Table 15 - WriteMemStacked Command SCD-Fields

# 4.4.9. WriteMemStacked Acknowledge

The WriteMemStacked acknowledge states the result of a WriteMemStacked command.

| Width   | Offset  | Description                                                          |

|---------|---------|----------------------------------------------------------------------|

| (Bytes) | (Bytes) |                                                                      |

|         |         | Prefix                                                               |

|         | CCD-    | ACK (command_id = WRITEMEM_STACKED_ACK)                              |

| 2       | 0       | Reserved                                                             |

|         |         | Reserved, set to 0                                                   |